台积电在2纳米工艺制程的竞赛中再次领先。12月6日,据中国台湾媒体报道,台积电已在新竹县宝山工厂完成2纳米制程晶圆的试生产工作,良品率高达60%,远超公司内部预期。台积电董事长魏哲家曾表示,2纳米制程市场需求巨大,客户订单可能超过3纳米制程。

台积电规划了新竹和高雄两地至少四座工厂用于2纳米制程生产,在满产状态下,到2026年初总产能将达12万片晶圆。在三星工艺开发受挫、英特尔代工业务前景不明的情况下,台积电在芯片代工行业已取得明显优势。

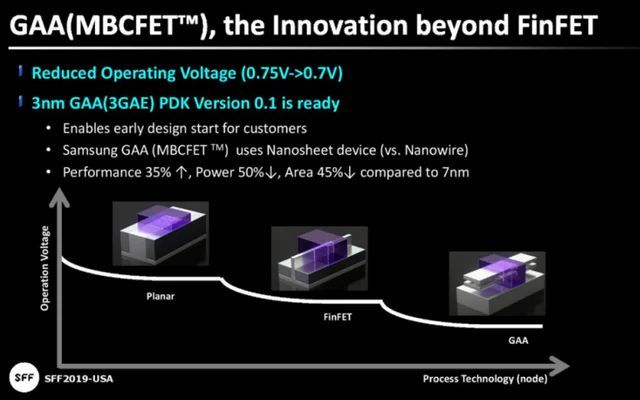

进入先进制程后,2纳米节点被视为关键节点。传统的FinFET架构在此尺度下开始失效,CMOS器件的短沟道效应问题再次凸显。为解决这一问题,华人科学家胡正明提出了鳍式场效应晶体管(FinFET)架构,使摩尔定律得以延续近20年。然而,进入5纳米工艺制程后,FinFET架构也开始逐渐失效,GAAFET架构应运而生。GAAFET架构通过旋转栅极鳍片并在垂直方向上分多条鳍片,增加了与沟道的接触面积。

台积电在开发3纳米工艺时选择继续优化FinFET结构,取得了良好效果。苹果A17芯片等使用台积电3纳米工艺的产品未出现明显发热或高功耗问题,良率也达到80%以上。相比之下,三星在3纳米工艺上直接采用GAAFET架构,但因开发难度大且时间紧迫,良率不足20%,无法满足量产需求。这使得台积电几乎包揽了全球3纳米芯片产能,三季度财报显示,其营收和净利润分别增长36.27%和50.18%。

在3纳米工艺代工获得丰厚收益后,台积电在2纳米工艺上的开发更加从容。台积电此前公布的路线图显示,N2工艺在相同功耗下性能比N3E提升10%-15%,而在相同性能下功耗降低25%-30%。尽管2纳米工艺代工价格预计高达3万美元,但对消费电子芯片厂商尤其是SoC设计厂商仍有巨大吸引力。

2纳米芯片的研发费用预计高达数十亿美元,这些成本最终将转嫁给消费者。台积电在芯片代工行业中已形成垄断地位,今年两次提高代工费用,不仅针对3纳米工艺,甚至5纳米工艺的价格也上调4%-10%。

三星电子在3纳米工艺上受挫后,计划全力投入2纳米工艺,但预计至少要到2027年才能实现量产。英特尔虽然完成了18A工艺(等效2纳米)的试生产,但良率过低且公司处于动荡期,量产时间不确定。因此,在2纳米工艺制程开发上,台积电的竞争对手目前难以匹敌,下游厂商在未来相当长一段时间内只能接受台积电的高价。

———END———

限 时 特 惠: 本站每日持续更新海量各大内部创业教程,一年会员只需168元,整站资源免费下载 点击查看详情

站 长 微 信: Jmbaoku